|

FPGA games

|

|

| RW9UAO | Дата: Воскресенье, 24.05.2015, 19:11 | Сообщение # 1 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| в ближайшем времени мне могут понадобится навыки verilog. я этим делом уже занимался, поэтому дело пошло легче.

цель девайса там простая - складывать в набортную память отсчеты АЦП. прям в ФПГА я могу получить 4096 32 битных слов блочной памяти. в аккурат два АЦП и еще останется.

садиться сразу за боевой проект чет я побоялся. заодно захотелось странного. народ активно занимается ретро компами. я решил глянуть одним глазом.

был вариант взять softcore i8080 (или даже КР580ВМ80) и в оставшееся место ФПГА запилить работу с памятью, генерацию видео и сделать "РАДИО86РК" или даже "СПЕЦИАЛИСТ". что-то побоялся я сразу такое сложное делать.

еще есть вариант взять чип КР580ВМ80 и прикрутить его к ФПГА, а уже в ФПГА эмулировать остальное железо. остановили следующие вещи: 3 питания (решается просто), отсутствие страшной ГФ24 в комплекте (тоже решается) и напроч не толерантная к 5ти вольтовым сигналам ФПГА (тоже решается), не особое мною понимание архитектуры 86РК, кривые исходники и кривые компиляторы под ВМ80.

Z80 со времен спектрума кажется задуренным. хотя "СПЕКТРУМ" можно было сотворить и погамать =)

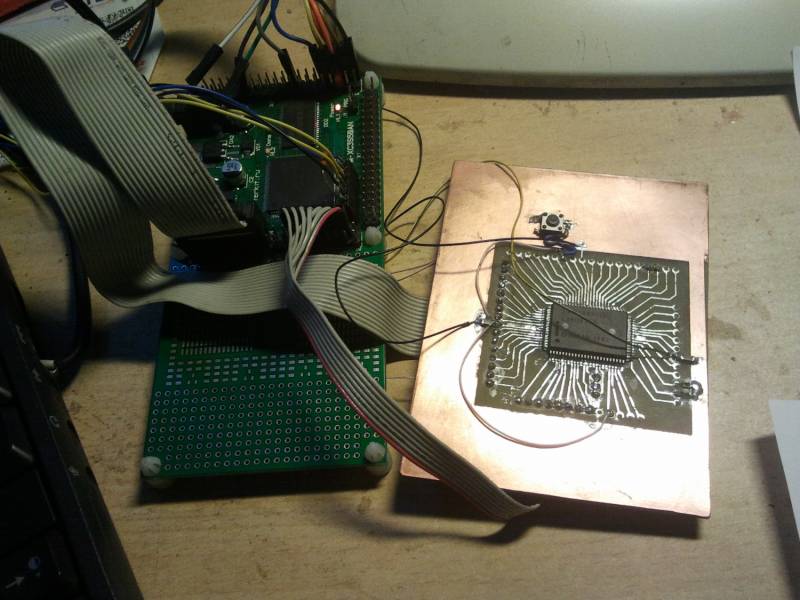

нарыл в закромах S80C188. он х86 совместимый программно. точнее 8080-80866 совместимый. это вроде как IBM-PC/XT или АТ, не помню. проц тоже насквозь 5ти вольтовый, но я применил грязный хак и запитал его от 3.3 вольта. проц как ни странно завелся на своей родной плате и вроде даже со всеми потрохами. я за полдня развел и сделал монтажку под него и прикрутил к ФПГА.

следующим шагом стала сборка BIOS от древних компов. нарыл исходники их и MASM4.0 которым оно собиралось в древности. кое-то даже собралось. есть нормальные исходники минимальной BIOS для S80C188, их применяли как микроконтроллеры =)

|

| |

| |

| RW9UAO | Дата: Воскресенье, 24.05.2015, 19:20 | Сообщение # 2 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

|

аппаратная часть готова.

и подключена к программатору. в роли программатора DELL пень233, который со мной лет 20.

с программаторами для XILINX целая песня. есть ногодрыг на FTDI, но для него кривой софт и сам по себе процесс ногодрыга очень медленный.

потом я нарыл проект JTAG на ородруине. как и все гавно на этой платформе оно годилось только для однократной прошивки мелких CPLD один раз из 100 попыток. переделка софта под standalone помогла не особо. CPLD шьет, а ФПГА медленно, печально и с постоянными вылетами.

потом я решил запустить проект USB-LPT на чипе от cypress на котором собран логический анализатор. делов-то, припаять другую EEPROM и прошить штатными утилитами. тоже засада, прошивается, но не запускается. бросил.

вернулся к xilinx JTAG LPT cable на аппаратном ЛПТ порту. вроде говорят PCI ЛПТ тоже работает.

хочу еще попробовать вариант с AT90USB192 или как-то так. или уже разориться на нормальный клон программатора (а до кучи еще и спартан6).

|

| |

| |

| RW9UAO | Дата: Воскресенье, 24.05.2015, 19:38 | Сообщение # 3 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

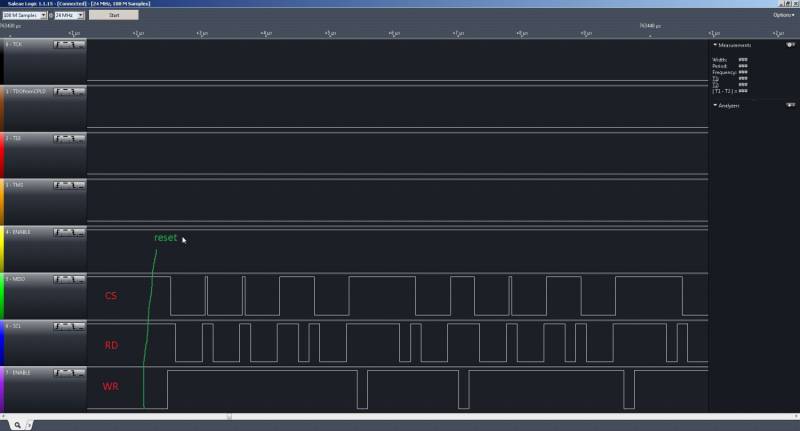

| начал описывать логику работы. шина адреса-данных у с188 мультиплексирована сигналом ALE. первым делом сделал полную шину адреса для чипа SRAM напаянного на devboard.

посмотрел как оно ведет себя на чипе.

после сброса идут обращения к памяти по адресу 0xFFF0, видно, что выставляется сигнал /CS (это UCS - выбор ROM памяти программ), выставляется сигнал /RD для чипа ROM, разрешая ей выдать байтик на шину данных (иначе ПЗУха держит шину данных в Z состоянии).

потом видно, что проц читает фигню и начинает дурить и изредка выставляет сигнал /WR. куда-то он пишет, но не в ROM, ибо его /CS не активен (в 1ке).

ну что-ж подсунем процу ПЗУху. есть у меня хитрая FRAM, но на 32 кб, а мне надо на 64. БИОС собирается в 64 кб образ. можно поставить флэшку, у меня их есть. но тогда процесс отладки будет такой. собрали прошивку, прошили чип в программаторе, поставили чип в плату, включили, видим ошибку, повторить. ыыыыыы.

можно взять чип SRAM на 64 кб (интересно, заведется ли он от 3.3 вольта, не хочется городить level-converter), и в ФПГА сделать процедуру загрузки этого чипа из компутера. по SPI грузим адрес и байт данных, дергаем ногой - записывается, идем дальше. 64 кб загрузятся за пару секунд.

еще можно захватить часть из 512 кб установленной чипы ОЗУ, грузить ее также. но все равно прийдется что-то разместить по адресу ресета.

я разместил bootROM в блочной памяти. при сбросе получаю управление в эту область. там размещается команда перехода по любому адресу. туда где будет лежать основная программа.

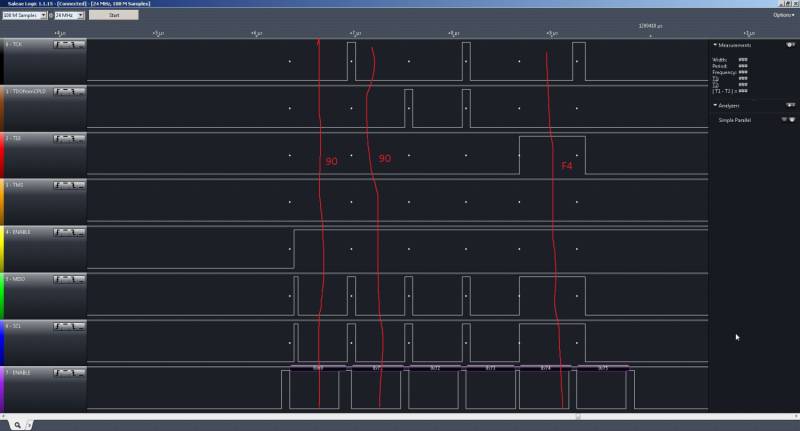

я накидал в bootROM программку

проц должен повиснуть на 5й команде. что собственно и происходит =)

NOP - 0x90

в 7м канале анализатора сигнал ALE. по спаду защелкивается адрес ПЗУ, по низкому уровню читается код команды из ПЗУ.

что видим:

по адресу 0xF0 команда 0x90

по адресу 0xF1 команда 0x90

по адресу 0xF2 команда 0x90

по адресу 0xF3 команда 0x90

по адресу 0xF4 команда 0xF4 (HLT) после которой процессор читает еще одну команду и повисает.

УРА! ЗАРАБОТАЛО!

теперь я в bootROM могу разместить переход на код загружаемый в ОЗУ сторонним сопроцессором и таким образом отлаживать программу не дергая чип флэшки в программатор и обратно.

|

| |

| |

| Mikele_P | Дата: Понедельник, 25.05.2015, 08:22 | Сообщение # 4 |

Свой Чувак !!!

Группа: Модераторы

Сообщений: 1468

Статус: Offline

| Цитата RW9UAO (  ) нарыл в закромах S80C188. он х86 совместимый программно. точнее 8080-80866 совместимый. это вроде как IBM-PC/XT или АТ, не помню.

Будешь пытаться полностью замоделировать ХТшку? Помнится был самодельный Русский вариант. Звался ПК "Поиск". Он там, кажись, на простейшей логике. Может поможет.

=============================================================

Воздух держит только тех, кто на него рассчитывает

=============================================================

Сообщение отредактировал Mikele_P - Понедельник, 25.05.2015, 08:23 |

| |

| |

| RW9UAO | Дата: Вторник, 26.05.2015, 15:03 | Сообщение # 5 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| отказался от bootROM расположенного в ФПГА.

напаял микросхему SRAM в 512 кб объемом для BIOS, пока размещу только верхние 64 кб. шина адреса, данных и сигнал /OE параллельно основной SRAM. /CS подключается на сигнал /UCS процессора.

набросал сдвиговый регистр для установки шины адреса и данных от внешнего процессора. идея такова:

- внешний процессор выставляет сигнал загрузки

- с188 уходит по этому сигналу в HOLD, либо просто отключается от шины адреса и данных мультиплексорами в ФПГА

- внешний процессор по SPI грузит 16 бит адреса и 8 бит данных в сдвиговый регистр

- выход сдвигового регистра подключен через мультиплексор (или через буфер с Z состоянием) к шине адреса и данных

- нога /UCS постоянно в низком уровне, чип выбран. /LCS постоянно в высоком уровне, чтобы не мешаться.

- внешний процессор дергает ногой /WR записывая данные по выбранному адресу.

- по окночани внешний процессор убирает сигнал загрузки и по желанию перезагружает с188.

|

| |

| |

| vikctc | Дата: Вторник, 26.05.2015, 15:06 | Сообщение # 6 |

Генерал

Группа: Модераторы

Сообщений: 1745

Статус: Offline

| Цитата Mikele_P (  ) Помнится был самодельный Русский вариант. Звался ПК "Поиск"

|

| |

| |

| Mikele_P | Дата: Вторник, 26.05.2015, 19:48 | Сообщение # 7 |

Свой Чувак !!!

Группа: Модераторы

Сообщений: 1468

Статус: Offline

| Цитата vikctc (  ) Ну уж и самодельный! вполне заводской

Я его видел и в сборе и в виде рассыпухи. Если учесть, что к нему прислюнявливали кассетный накопитель на видеокассете, то точно самопал на 80-99%.

=============================================================

Воздух держит только тех, кто на него рассчитывает

=============================================================

|

| |

| |

| RW9UAO | Дата: Вторник, 26.05.2015, 21:26 | Сообщение # 8 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| кое-никак упихал в ФПГА следующий дизайн:

- внешний процессор выставляет сигнал загрузки ROM_load_EN в 1, одновременно с188 переводит в HOLD, чтобы не мешался.

- нога /CS ROM постоянно в низком уровне, чип выбран. /CS SRAM постоянно в высоком уровне, чтобы не мешался.

- адресная шина SRAM и ROM мультиплексором переключается на сдвиговый регистр.

- к шине данных SRAM и ROM подключается младшая часть сдвигового регистра.

начало цикла

- внешний процессор по SPI грузит 16 бит адреса и 8 бит данных в сдвиговый регистр.

- внешний процессор дергает ногой /WR записывая данные по выбранному адресу.

конец цикла

- внешний процессор убирает сигнал загрузки

- /CS памяти возвращаются владельцам

- адресная шина SRAM и ROM мультиплексором переключается на регистр шины адреса.

- младшая часть сдвигового регистра переходит в Z состояние.

- нажимаем кнопку RESET c188 =)

|

| |

| |

| Mikele_P | Дата: Четверг, 28.05.2015, 17:09 | Сообщение # 9 |

Свой Чувак !!!

Группа: Модераторы

Сообщений: 1468

Статус: Offline

| Чесслова... Хоть бы принципиалку кинул, а... А так чё там RAS чё там "DVA" -- не ясно даже близко. Я вот только понял, что ты как-то паметюху приколхозил и что-то типа DMA-хи

=============================================================

Воздух держит только тех, кто на него рассчитывает

=============================================================

|

| |

| |

| RW9UAO | Дата: Четверг, 28.05.2015, 21:17 | Сообщение # 10 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| хе, схему.....

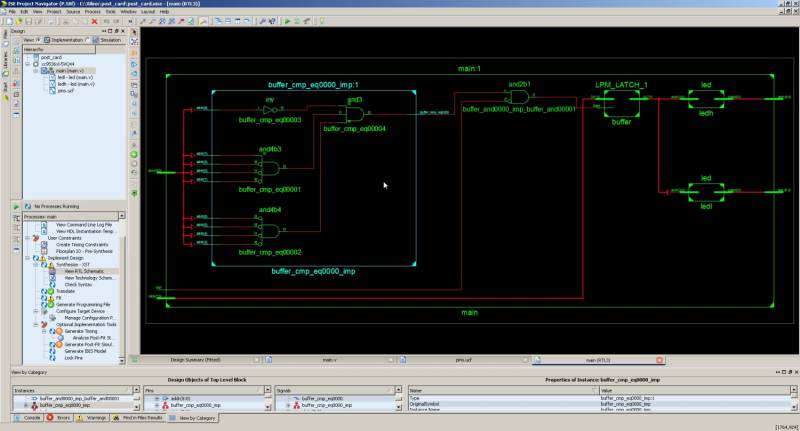

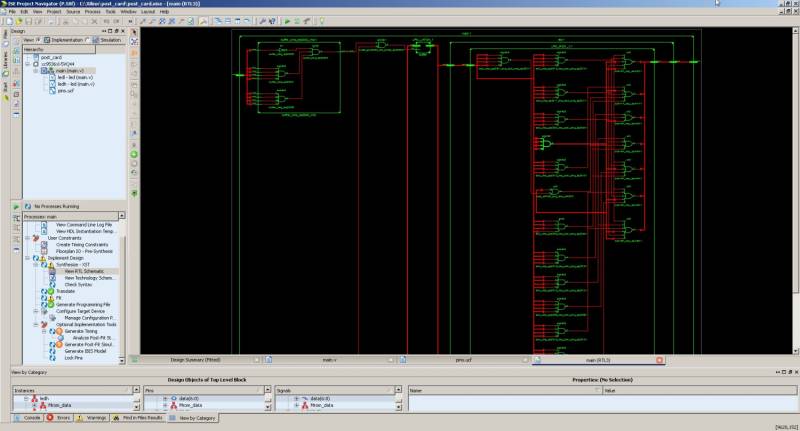

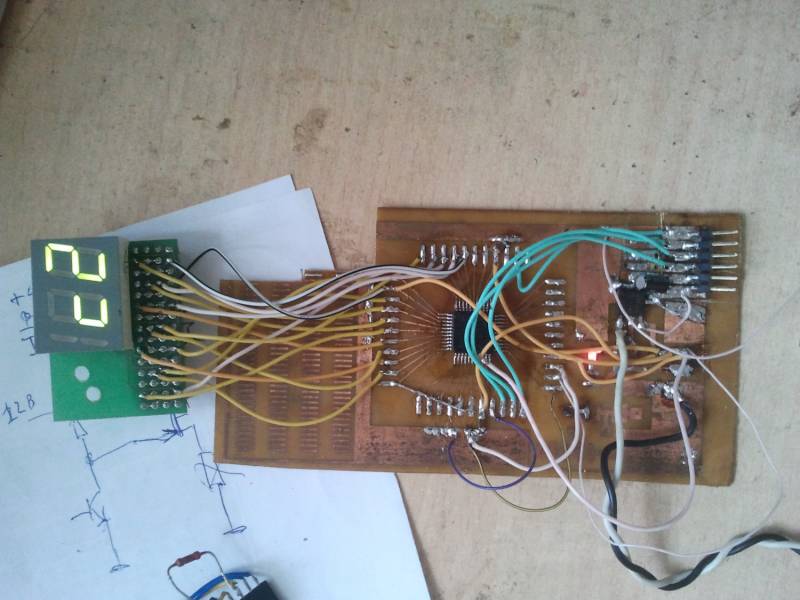

практическая поделка на CPLD на verilog

завалялась у меня материнка 486, странная, то заводится, то нет. решил я для нее ISA POST карту сделать. но не на рассыпухе к1553 серии, а в программируемой логике. и не в схематике (это когда схему рисуешь из 74НС серии и прошиваешь в чип), а на язык описания.

делов-то сравнить входной адрес с 0х80 и защелкнуть шину данных в регистр по сигналу записи в порт IOW.

после синтеза получилась такая схема:

шина адреса на входе сравнивается с нужным значением с помощью И логики. некоторые входа инвертированы =)

запись в регистр сделал по уровню, а не по спаду сигнала IOW.

после регистра стоят два декодера 7ми сегментного индикатора.

тут я развернул один из макроблоков - декодера. при таком раскладе смысл схемы теряется. максимум можно понять как соединяются макроблоки.

|

| |

| |

| RW9UAO | Дата: Четверг, 28.05.2015, 21:20 | Сообщение # 11 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

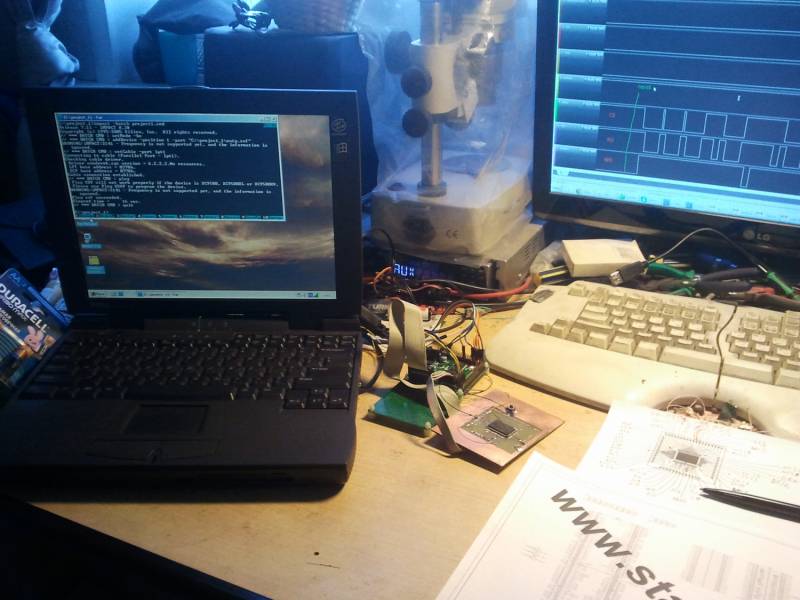

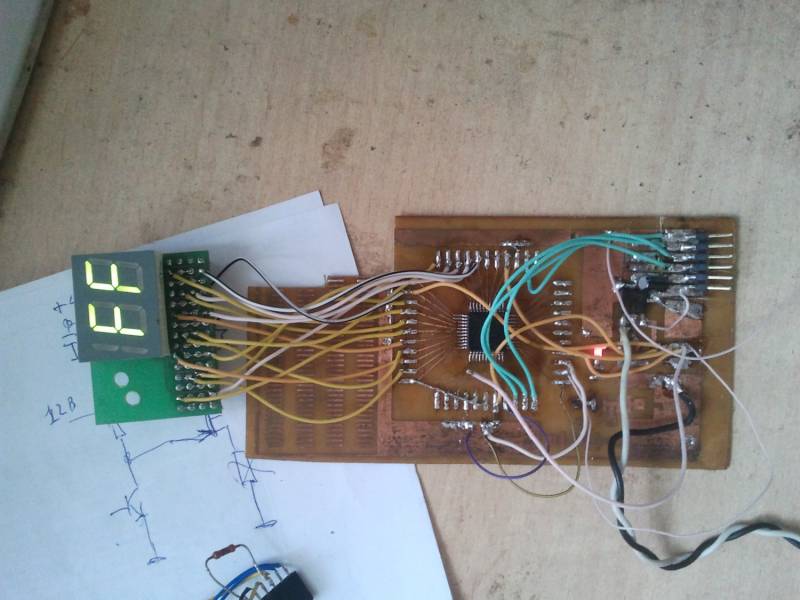

| можно было сделать test-bench и прогнать в симуляторе, но это не наш метод.

в закромах нашел какую-то старую монтажку с похожим пинаутом. спаял за вечер схему и прошил чип.

перемычками временно задан нужный адрес, а шину данных я эмулирую пинцетом.

|

| |

| |

| RW9UAO | Дата: Четверг, 28.05.2015, 21:22 | Сообщение # 12 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

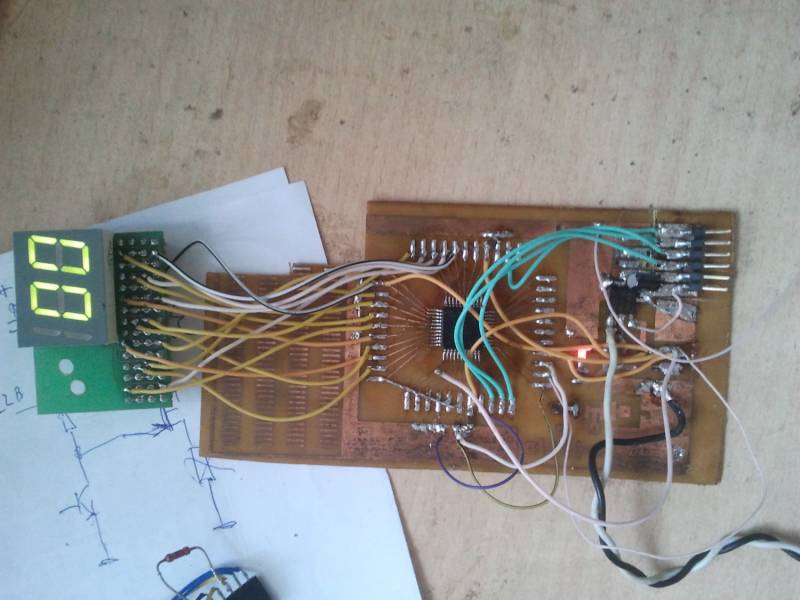

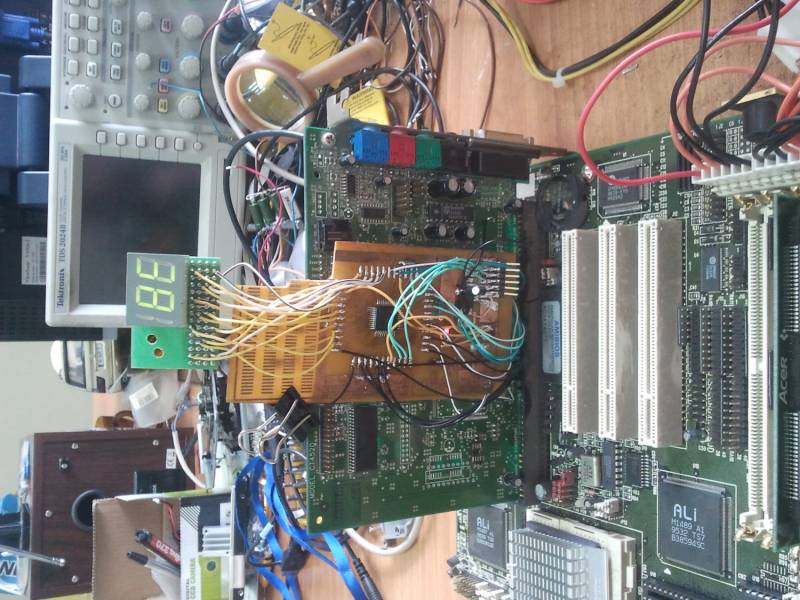

| по ходу пьесы наткнулся на неисправную ножку CPLD, она постоянно считывалась как "1". чип выпаян из дохлого девайса, видимо досталось ему.

в файле расстановки выводов перенес сигнал на соседнюю ножку и все заработало корректно. прелесть программируемой логики.

чип толерантен к 5в входным сигналам и имеет достаточную нагрузочную способность, чтобы напрямую светить светодиодами.

|

| |

| |

| RW9UAO | Дата: Пятница, 29.05.2015, 11:02 | Сообщение # 13 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| фотографии в интерьере

из описания AMIBIOS "Возврат в реальный режим адресации памяти. Ранняя инициализация чип сета.Установка стека"

после установки памяти. не понятный код. видеокарта не установлена

"Видеорежим установлен. Экран очищен"

|

| |

| |

| vikctc | Дата: Пятница, 29.05.2015, 20:34 | Сообщение # 14 |

Генерал

Группа: Модераторы

Сообщений: 1745

Статус: Offline

| Mikele_P, Вот!!! Это ОН "Поиск"  . Серега давай к нему катушечный магнитофон прикрутим. У меня где то в гараже Сатурн 201 завалялся. . Серега давай к нему катушечный магнитофон прикрутим. У меня где то в гараже Сатурн 201 завалялся.

|

| |

| |

| RW9UAO | Дата: Пятница, 29.05.2015, 20:43 | Сообщение # 15 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| это 486DX133 =)

|

| |

| |