|

FPGA games

|

|

| vikctc | Дата: Пятница, 29.05.2015, 22:11 | Сообщение # 16 |

Генерал

Группа: Модераторы

Сообщений: 1745

Статус: Offline

| Цитата RW9UAO (  ) то 486DX133 =)

|

| |

| |

| Maloy | Дата: Суббота, 30.05.2015, 10:17 | Сообщение # 17 |

Генерал

Группа: Moderator

Сообщений: 1653

Статус: Offline

| у всех прогресс

а ретро лучше

С Уважением Владимир ! Мозг - это тормоз, чувства - это газ. Главное - найти сцепление,,,

|

| |

| |

| RW9UAO | Дата: Понедельник, 08.06.2015, 12:06 | Сообщение # 18 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| выбрал вечер свободного времени. допилил проект эмулятора ПЗУ BIOS.

отвязал мультиплексором шину адреса и еще одним мультиплексором шину данных чипа SRAM, последовательно в сдвиговый регистр загружаю адрес и данные. 64 кб образ льется за 1 минуту. нормально.

образ XTBIOS собирается из исходников, пришлось его немного доработать. bootloader по умолчанию должен занимать 1 кб кода, пришлось по входу точки сброса прописать переинициализацию регистра управляющего сигналом CS ROM BIOS. ради этого пришлось выкинуть строку версии BIOS.

также надо доработать инициализацию CS выбора чипа RAM, по умолчанию 256 кб, у меня 512 кб нижней памяти.

в итоге образ BIOS частично запустился. пробежался по тестам и ушел в HLT по какой-то причине. ибо нет дешифрации портов ввода-вывода и не понятно, чего там откуда читается.

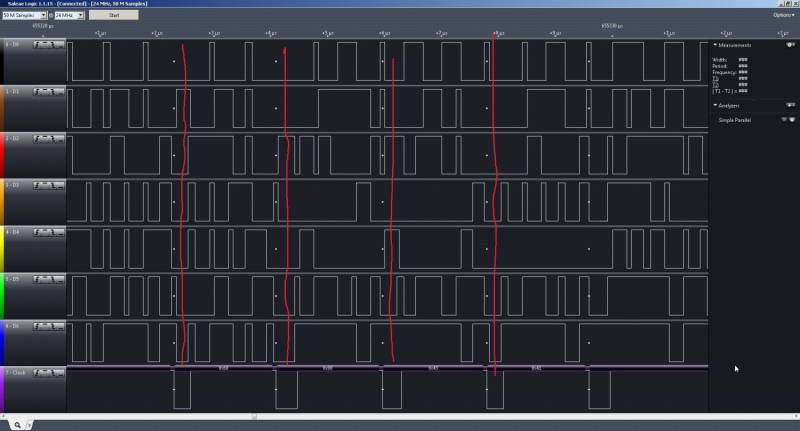

занялся функционалом отладки. я хочу на лог анализаторе видеть всю шину адреса. ну или хотябы 12 бит ее. а ширина ЛА - 8 бит.

пока дошел до следующего: по спаду сигнала ALE отдавать по 4 бита шины адреса в debug порт с выводом clock синхронизации еще в один бит. уперся в недостаток скорости. 80 мгц мало, или мой ЛА не успевает защелкнуть все что выше 24 мгц. буду думать дальше.

|

| |

| |

| RW9UAO | Дата: Понедельник, 08.06.2015, 21:35 | Сообщение # 19 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| вобщем ничего у меня с дебагом путнего не вышло. решил сделать проще. засинхронизировался по сигналу ALE и считал шину адреса по 4 бита. зависаю я примерно в одном месте.

и вот что получилось

Код E0D5: 75

E0D6: D4 JNZ E0AB

E0D7: неважно, так работает механизм выборки инструкции

E0AB: F4 HLT

Код ;----------------------------------------

; ROS CHECKSUM TEST I :

;DESCRIPTION :

; A CHECKSUM IS DONE FOR THE 8K :

; ROS MODULE CONTAINING POD AND :

; BIOS. :

;----------------------------------------

; ZERO IN AL ALREADY

OUT 0A0H,AL ; DISABLE NMI INTERRUPTS

OUT 83H,AL ; INITIALIZE DMA PAGE REG

MOV DX,3D8H

OUT DX,AL ; DISABLE COLOR VIDEO

INC AL

MOV DL,0B8H

OUT DX,AL ; DISABLE B/W VIDEO,EN HIGH RES

MOV AL,89H ; SET 8255 FOR B,A=OUT, C=IN

OUT CMD_PORT,AL

MOV AL,10100101B

; ENABLE PARITY CHECKERS AND

OUT PORT_B,AL ; PULL KB CLOCK HI, TRI-STATE

; KEYBOARD INPUTS,ENABLE HIGH

; BANK OF SWITCHES->PORT C(0-3)

MOV AL,01H ; <><><><><><><><><><><><>

OUT PORT_A,AL ; <><><>CHECKPOINT 1<><><>

MOV AX,CS ; SETUP SS SEG REG

MOV SS,AX

MOV DS,AX ; SET UP DATA SEG TO POINT TO

; ROM ADDRESS

CLD ; SET DIRECTION FLAG TO INC.

ASSUME SS:CODE

MOV BX,00000H ; SETUP STARTING ROS ADDR

MOV SP,OFFSET C1 ; SETUP RETURN ADDRESS

JMP ROS_CHECKSUM

[b]C11:

[b]JNE ERR01 ; HALT SYSTEM IF ERROR

MOV SP,OFFSET C1 ; SETUP RETURN ADDRESS

значит что-то пошло не так в функции "ROS_CHECKSUM". она просто XORит байтики по адресу который лежит в BX и возвращает флаг Z. на который я и реагирую переходом на ERR01.

надо как-то более оперативно все-же адрес считывать. думаю как.

|

| |

| |

| RW9UAO | Дата: Понедельник, 08.06.2015, 22:02 | Сообщение # 20 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| отключил проверку контрольной суммы BIOS, теперь она всегда верная =)

уткнулся в другую проверку:

Код ;----- VERIFY THAT TIMER 1 FUNCTIONS OK |

| |

| |

| RW9UAO | Дата: Понедельник, 15.06.2015, 17:19 | Сообщение # 21 |

Генерал

Группа: Проверенные

Сообщений: 2085

Статус: Offline

| по быстрому набросал механизм выборки IOWR-IORD, сигналов записи-чтения внешних устройств.

засинхронизировался по сигналу IOWR и вижу, что была запись в порты:

0х60 значения 0х02

0х08 значения 0х04

0х43 значения 0х54

0х41 значения 0х00

что вполне совпадает с исходником

Цитата MOV AL,02H

OUT PORT_A,AL ;060H ; KEYBOARD SCAN CODE/CONTROL PORT

MOV AL,04

OUT DMA08,AL ; 008H ; DMA STATUS REGISTER PORT ADDRESS

MOV AL,54H ; SEL TIMER 1,LSB,MODE 2

OUT TIMER+3,AL ; 043H ; 8253 TIMER CONTROL PORT ADDR

MOV AL,CL ; SET INITIAL TIMER CNT TO 0

OUT TIMER+1,AL |

| |

| |